Les semi-conducteurs à l’intérieur de nos CPU sont gravés toujours un peu plus finement, certes. Mais la tendance est au ralentissement, à cause des limites physiques et des contraintes économiques. A moins de sonner le glas du silicium ou de généraliser l’informatique quantique.

La miniaturisation des semi-conducteurs et des circuits intégrés, dont les CPU et GPU qui équipent nos PC et nos smartphones, connaîtra-t-elle bientôt un coup d’arrêt ? A la lumière de l’actualité récente, la question paraît saugrenue, tant la gravure des micro-composants électroniques ne cesse de s’affiner. Le fondeur TSMC prévoit d’ouvrir des lignes de production à 5 nanomètres (nm) dont Apple devrait être un bénéficiaire de premier rang.

De son côté, Samsung a validé ses outils de conception dédiés aux composants à 5 nm et a déjà communiqué sur la fabrication à 3 nm. C’est à croire que les procédés les plus répandus aujourd’hui pour les circuits intégrés à haute densité – 14 nm, 10 nm (mis en œuvre par Intel notamment avec les CPU Ice Lake) voire 7 nm – vont tomber en désuétude d’ici à quelques années.

Cette vidéo explique le principe de fonctionnement d’un transistor à effet de champ MOS, ou MOSFET (metal oxyde semiconductor field effect transistor). C’est la brique élémentaire des circuits intégrés à haute densité, comme les CPU.

Pourtant, cette évolution ne pouvait se poursuivre indéfiniment, nous disait-on, à cause de limites physiques infranchissables… Mais les services marketing empruntent des chemins détournés pour livrer des chiffres flatteurs, voire trompeurs. « La terminologie employée ne correspond plus forcément à une dimension mesurée sur le circuit intégré, indique Olivier Faynot, chef du service Patterning au CEA Leti (Commissariat à l’énergie atomique, Laboratoire d’électronique et de technologie de l’information). Historiquement, quand on parlait d’un nœud à 28 nm (dans le jargon du métier, un nœud constitue une étape technologique, ndlr), cette valeur reflétait une grandeur physique, à savoir la longueur de la grille du transistor. Désormais, quand un industriel évoque un nœud de 5 ou 7 nm, les dimensions sont plutôt de l’ordre de 10 nm. »

Quand le robinet à électrons fuit

Et il sera très compliqué d’aller en-deçà. À ce point minuscule, un transistor, qui se compare à un robinet à électrons, fuit en permanence. « Quand il est trop petit, les électrons peuvent transiter de la source au drain par effet tunnel, ce qui intensifie les courants de fuite » explique Olivier Faynot. Il est alors impossible de distinguer un état ouvert d’un état fermé, ce qui est la base du circuit logique auquel appartient ce transistor.

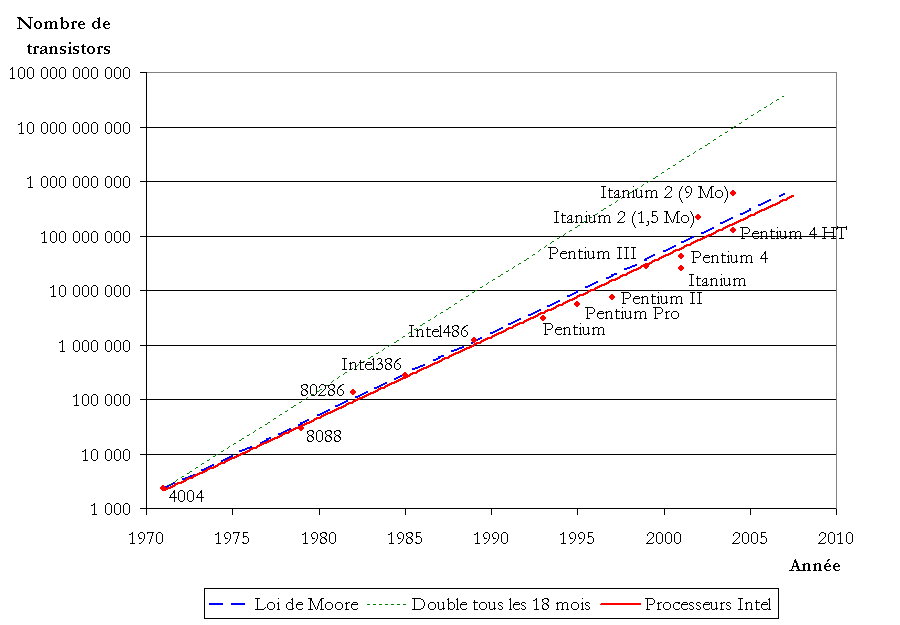

La Loi de Moore (©QcRef87)

De fait, la courbe qui exprime la fameuse loi de Moore, énoncée en 1965 par l’ingénieur du même nom, s’infléchit depuis plusieurs années. « D’un nœud technologique au suivant, les performances s’amélioraient de 30% et la surface du circuit intégré diminuait de moitié, à nombre de transistors égaux, poursuit Olivier Faynot. Ces règles s’appliquaient encore jusqu’à 28 nm (introduit à partir de 2011, ndlr). Depuis, les industriels éprouvent des difficultés à les respecter. »

Rapprocher les transistors

La miniaturisation ne s’arrête pas, ceci-dit, mais s’exerce ailleurs. « On rapproche les transistors et on raccourcit leurs interconnexions, de façon à ce que la taille globale du circuit diminue, précise Olivier Faynot. Mais comme les lignes qui conduisent l’électricité se rapprochent, des capacités parasites se manifestent et impliquent de réduire les constantes diélectriques entre ces lignes. Faute de quoi, les performances du circuit intégré sont moindres. »

L’architecture du transistor s’est également perfectionnée au fil des années afin que la taille des circuits continue à se réduire. Les premiers circuits avec des transistors à effet de champ à ailette (FinFET, parfois appelé transistor 3D) ont été commercialisés à partir de 2012, au moment du passage au 22 nm.

Le transistor GAAFET (gate all around field effect transistor), en quelque sorte un dérivé du FinFET, permettra d’atteindre les nœuds à 5 et 3 nm. « Le canal de conduction se réduit à un nanofil, détaille Olivier Faynot. On obtient ainsi un meilleur compromis entre le courant de fuite et le courant utile. En R&D, nous travaillons sur le sujet depuis des années. Le GAAFET sort des salles blanches de TSMC et Samsung désormais. »

Pour sa future production à 3 nm, Samsung a mis au point et breveté une nouvelle évolution de la famille de transistors GAAFET, nommée MBCFET. Par rapport aux circuits FinFET en 7nm, la consommation électrique serait moitié moindre et les performances 30 % supérieures.

Pour le 3 nm, Samsung a même annoncé un nouveau type de transistor voici quelques mois, le MBCFET (MBC signifiant multi bridge channel).

Schématiquement, les nanofils du GAAFET sont remplacés par des nanofeuilles, plus efficaces pour conduire le courant électrique. D’après Samsung, qui se réfère au FinFET en 7 nm, les circuits à base de MBCFET consommeraient moitié moins, occuperaient 45 % d’espace en moins, tout en offrant des performances supérieures de 30%.

Gros investissements et gains minimes

Dans cette industrie, une autre règle moins explicite est en vigueur : plus les circuits rapetissent, plus les industriels capables de les produire se font rare.

L’an dernier, GlobalFondries a jeté l’éponge pour se concentrer sur les nœuds à 12 nm et plus. Alors que les gains sont beaucoup moins spectaculaires que par le passé, les investissements sont colossaux en effet : les usines se chiffrent en plusieurs milliards d’euros, sans oublier « l’infrastructure et la conception du circuit, de plus en plus complexes, qui entrent dans l’équation » ajoute Olivier Faynot.

Pourra-t-on descendre en dessous du nœud à 3 nm ? Avec le silicium, la réponse est vraisemblablement négative. D’où l’idée d’exploiter d’autres matériaux, comme le graphène, pour constituer le transistor du futur. Mais ces pistes demeurent très expérimentales. L’informatique quantique est peut-être plus prometteuse, car elle implique un changement de paradigme.

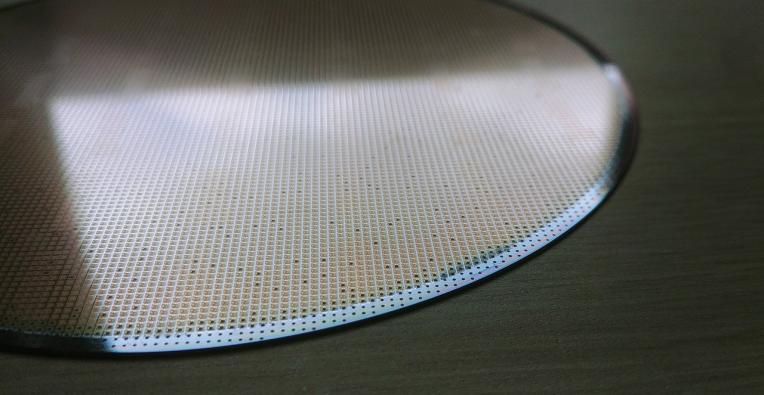

« Chercher à réduire les dimensions, c’est s’exposer à un gouffre économique, à des limites physiques et à des défauts d’uniformité sur les wafers (galettes de silicium où sont gravés les circuits intégrés, ndlr). L’informatique quantique offre une alternative : l’information est différenciée par l’état quantique des électrons. Mais beaucoup d’autres contraintes sont à surmonter. »

Les choses avancent vite cependant : il y a quelques jours, IBM a annoncé le lancement d’un ordinateur d’une puissance de 53 qbits.